Thông tin tài liệu

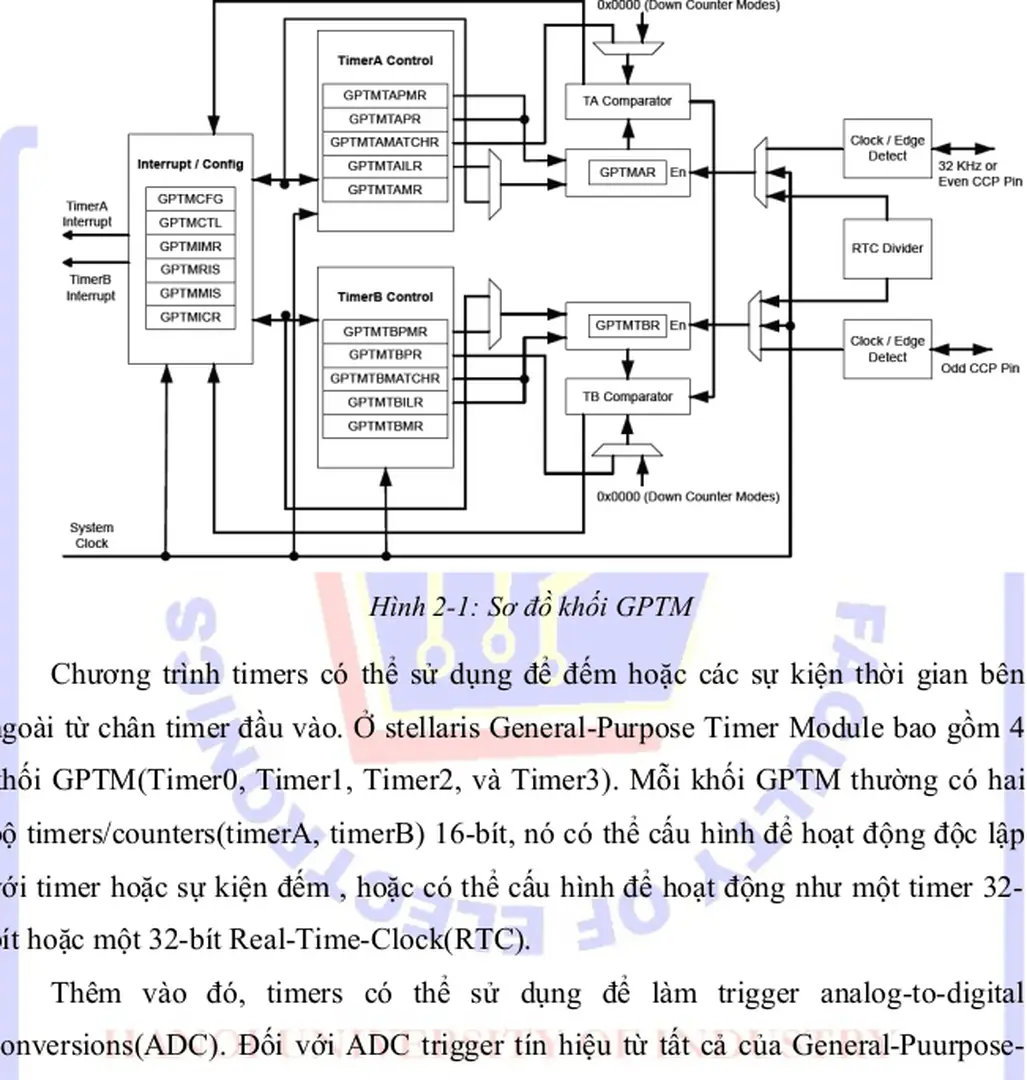

Ha Noi university of industry FEE2-K2 BỘ CÔNG THƯƠNG TRƯỜNG ĐẠI HỌC CÔNG NGHIỆP HÀ NỘI KHOA : ĐIỆN TỬ NGHIÊN CỨU, MÔ PHỎNG HOẠT ĐỘNG CỦA TIMER, INTERRUPT, ADC, UARTS, SSI, I2C, CAN TRÊN VI ĐIỀU KHIỂN ARM CORTEX-M3 LM3S8962 CỦA HÃNG TEXAS INTSTRUMENTS Giáo viên hướng dẫn: Phạm Văn Chiến Sinh viên thực hiện: Nguyễn Văn Tấn Trương Đình Hà Lớp: ĐH CNKT ĐT2- K2 Hà Nội – 06/201 _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Mục lục Chương V Giao diện liên vi mạch (I2C) 42 Chương VII : Bộ chuyển đổi tương tự - số (ADC) 69 7.4 Bản đồ ghi 77 Chương VIII: UARTs 79 8.1 Sơ đồ khối 80 8.2 Mô tả chức 80 8.2.2 Tốc độ baud .81 _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Lời mở đầu Ngày nay, dòng vi điều khiển ngày có vị trí quan trọng lĩnh vực điện tử, khơng khó để nhận hầu hết lĩnh vực đời sống có tham gia vi điều khiển Có nhiều ho vi điều khiển để nghiên cứu, tìm hiểu ứng dụng như: 8051, PIC, PSoc, AVR… Trong nhiều năm trước, dòng vi điều khiển 8051 sinh viên sử dụng nhiều với tính đơn giản, dễ sử dụng; AVR sử dụng nhiều thi Robocon nhờ tốc độ xử lý cao, ổn định; PIC với ưu tốc độ cao, chi phí thấp nghiên cứu, sử dụng nhiều, đặc biệt thi lập trình tay nghề khu vực giới… Nhưng vài năm trở lại đây, có dịng vi điều khiển mới, ngày nắm vị trí quan trọng lĩnh vực đòi hỏi tốc độ xử lý cao điện tử viễn thơng, giám sát, an ninh… Đó họ vi điều khiển ARM Với nhiều hệ đời, với nhiều tính năng, cơng dụng khác Tình hình nghiên cứu ở nước ngồi: Chíp ARM nghiên cứu phát triển ứng dụng rộng rãi đo lường điều khiển Đặc biệt chíp ARM nghiên cứu ứng dụng để sản xuất thiết bị cầm tay điện thoại, máy ảnh thiết bị đòi hỏi tốc độ xử lý cao tivi, thiết bị xử lý tín hiệu số… Các hãng sản xuất chíp đưa vào nhiều ngoại vi để phục vụ mục đích giao tiếp, đo lường điều khiển ngưởi phát triển ứng dụng Tình hình nghiên cứu ở nước: Chíp ARM cá nhân cố công ty nghiên cứa ứng dụng, Nhưng chưa trường đưa vào để giảng dạy cho sinh viên Bởi có kiến trúc phức tạp, nhiều chuẩn giao tiếp tài nguyên đại mà chưa nghiên cứu rộng rãi để ứng dụng Với nhiều tính vượt trội ARM xu lựa chọn dòng vi điều khiển Việt Nam nên đề tài nghiên cứu khoa học này, giúp đỡ Thầy Phạm Văn Chiến, thực đề tài nghiên cứu chip ARM Cortex M3 LM3S8962 hãng Texas Instruments _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Trong giới hạn thời gian cho phép, đồng thời có hạn chế nguồn tài liệu hỗ trợ nghiên cứu, đề tài nghiên cứu tơi cịn nhiều thiếu sót, cịn nhiều lỗi kỹ thuật báo cáo, nên mong đóng góp ý kiến Hội đồng bảo vệ thầy cô để đề tài nghiên cứu chúng tơi hồn thiện Cuối xin chân thành cảm ơn thầy Vũ Trung Kiên, thầy Phạm Văn Chiến, thầy Nguyễn Văn Tùng, thầy cô khoa Điện Tử anh Nguyễn Xuân Kiên- đại diện TI Việt Nam giúp chúng tơi hồn thành đề tài nghiên cứu này! Nhóm sinh viên thực Nguyễn Văn Tấn Trương Đình Hà _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Chương I: Tổng quan kiến trúc ARM Cortex M3 Các dòng vi điều khiển Stellaris – ARM ® ™ Cortex-M3 - mang lại ứng dụng vi điều khiển nhúng hiệu suất cao 32-bit Những phận tiên phong cung cấp cho khách hàng 32-bit hoạt động chi phí tương đương với vi điều khiển kế thừa bit 16bit Các Stellaris cung cấp hiệu suất hiệu hội nhập sâu rộng, thiết bị định vị thuận lợi với chi phí hợp lý, ứng dụng địi hỏi phải kiểm sốt q trình đáng kể khả kết nối Dịng Stellaris LM3S8000 kết hợp cơng nghệ Bosch Controller Area Network với 10/100 Ethernet Media Access Control (MAC) lớp vật lý (PHY) Các vi điều khiển LM3S8962 mục tiêu cho ứng dụng công nghiệp, bao gồm giám sát từ xa, máy bán điện tử, thiết bị kiểm tra đo lường, thiết bị mạng thiết bị chuyển mạch, nhà máy tự động hóa, HVAC kiểm sốt tịa nhà, thiết bị chơi game, điều khiển chuyển động, thiết bị y tế, cứu hỏa an ninh Đối với ứng dụng yêu cầu tiết kiệm lượng, LM3S8962 đề cao mô-đun pin hiệu theo, đưa lượng tiêu hao LM3S8962 đến trạng thái lượng thấp thời gian dài không hoạt động Với chuỗi power-up/power-down, đồng hồ thời gian thực lien tục (RTC), cặp ghi phù hợp, giao diện APB với bus hệ thống, nhớ không bay dành riêng, mô-đun Hibernation, vi điều khiển LM3S8962 hoàn hảo cho ứng dụng pin Ngoài ra, vi điều khiển LM3S8962 cung cấp lợi ARM phổ biến rộng rãi với công cụ phát triển, System-on-Chip (SoC) ứng dụng sở hạ tầng IP, cộng đồng lớn người dùng Ngồi ra, vi điều khiển ARM sử dụng Thumb ® tương thích Thumb-2 hướng dẫn thiết lập để giảm nhớ u cầu và, chi phí giảm theo Cuối cùng, vi điều khiển LM3S8962 mã tương thích cho tất thành viên gia đình Stellaris rộng, cung cấp linh hoạt để phù hợp xác nhu cầu khách hàng 1.1 Tính sản phẩm Các vi điều khiển LM3S8962 bao gồm tính sau: ■ 32-bit RISC _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 - 32-bit ARM Cortex ® ™-M3 v7M kiến trúc tối ưu hóa với chân linh kiện nhỏ cho ứng dụng nhúng - Hệ thống hẹn (SysTick), cung cấp đơn giản, 24-bit tự động nạp lại, tạo kiện ngắt đếm xuống mức zero, truy cập với chế điều khiển linh hoạt, thiết kế cho hệ điều hành thời gian thực - Thumb ® tương thích Thumb-2-nhằm đạt hiệu suất cao tập lệnh ARM-32bit với mật độ ma chương trình tối ưu tập lệnh Thumb 16bit - Hoạt động 50-MH - Chia phần cứng khuếch đại chu trình đơn - Tích hợp Bộ điều khiển vector ngắt lồng (NVIC) cung cấp tính định xử lý ngắt - 36 ngắt với tám cấp độ ưu tiên - Khối bảo vệ nhớ (MPU), cung cấp chế độ đặc quyền cho cấu trúc hệ điều hành bảo vệ - Truy cập liệu độc lập, cho phép liệu đóng gói vào nhớ hiệu - Thao tác bit (dải bit), cung cấp sử dụng nhớ tối đa kiểm soát thiết bị ngoại vi hợp lý ■ ARM Cortex ® ™-M3 Processor Core - Lõi thu gọn - Thumb-2, cung cấp tính cao dự kiến lõi ARM kích thước nhớ thường kết hợp với - 16-bit thiết bị; thường khoảng vài kilobyte nhớ cho ứng dụng lớp vi điều khiển - Nhanh chóng thực thơng qua ứng dụng kiến trúc Harvard bus đặc trưng riêng biệt cho điều khiển liệu - Xử lý gián đoạn vượt trội, cách thực thao tác ghi cần thiết để xử lý gián đoạn phần cứng - Tính định, xử lý ngắt nhanh chóng: 12 chu kỳ, có chu kỳ với kỹ thuật tail-chaining - Đơn vị bảo vệ nhớ (MPU) cung cấp chế độ ưu tiên để thực ứng dụng phức tạp _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 - Dịch chuyển từ gia đình xử lý ARM7 ™ cho hiệu tốt hiệu lượng - Đầy đủ tính giải pháp gỡ rối • JTAG Debug Serial Port (SWJ-DP) • Flash Patch Breakpoint (FPB) đơn vị để thực điểm ngắt • DataWatchpoint Trigger (DWT) đơn vị thực watchpoints, nguồn trigger hệ thống hồ sơ • Instrumentation Trace Macrocell (ITM) để hỗ trợ gỡ rối kiểu printf • Trace Port Interface Unit (TPIU) để chuyển tiếp đến Trace Port Analyzer - Tối ưu hóa cho việc sử dụng flash đơn chu kỳ - Ba chế độ ngủ với điện thấp - Hướng dẫn đơn chu kỳ phân chia phần cứng - Hoạt động nguyên tử - ARM Thumb2 16-/32-bit tập lệnh hỗn hợp - 1.25 DMIPS/MHz ■ JTAG - IEEE 1.149,1-1990 tương thích điều khiển Test Access Port (TAP) - Bốn-bit ghi điều khiển (IR) để lưu trữ thị JTAG - Tiêu chuẩn thị IEEE: BYPASS, IDCODE, SAMPLE/PRELOAD, EXTEST INTEST - ARM thêm thị: APACC, DPACC ABOR - Tích hợp ARM Serial Wire Debug (SWD) ■ Hibernation - Hệ thống điều khiển công suất sử dụng điều chỉnh bên riêng biệt - Pin chuyên dụng để báo tín hiệu bên ngồi - Phát pin thấp, báo hiệu tạo ngắt - Đồng hồ thời gian thực (RTC) 32-bit - Hai ghi RTC 32-bit phù hợp cho thức dậy tạo ngắt - Xung nhịp nguồn từ dao động bên 32,768-kHz thạch anh 4,194304-MHz - RTC vi chỉnh để điều chỉnh tốt với tỷ lệ xung nhịp _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 - 64 từ nhớ 32-bit không bay - Có thể lập trình ngắt cho RTC phù hợp, đánh thức bên ngoài, kiện pin thấp ■ Bộ nhớ - 256 KB flash - 64 kB SRAM ■ GPIOs - 5-42 GPIOs, tùy thuộc vào cấu hình - 5-V, tùy vào cấu hình đầu vào - Có thể lập trình điều khiển cho ngắt GPIO • Tạo ngắt • Gây ngắt theo sườn: lên, xuống hai • Ngắt theo mức : cao thấp - Đọc ghi hoạt động bit thơng qua dịng địa - Có thể bắt đầu chuỗi mẫu ADC - Các Pin cấu đầu vào kỹ thuật số Schmitt-Trigger - Có thể lập trình điều khiển để cấu hình chân GPIO • Điện trở kéo lên nguồn, kéo xuống mass • 2-mA, 4-mA, 8-mA để giao tiếp kỹ thuật số; cấu hình lên đến 18-mA cho ứng dụng cần dịng lớn • Cho phép đầu vào kỹ thuật số ■ General-Purpose Timers - General-Purpose Timer Modules (GPTM), cung cấp hai timer/counter 16-bit Mỗi GPTM cấu hình để hoạt động độc lập: • Là đếm thời gian 32-bit • Là đồng hồ thời gian thực 32-bit (RTC) để nắm bắt kiện • Dùng cho điều chế rộng xung (PWM) • Để kích hoạt chuyển đổi tương tự - số - Chế độ Timer 32-bit • Có thể lập trình one-shot thời gian • Có thể lập trình theo chu kỳ thời gian _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 • Real-Time Clock sử dụng xung nhịp 32,768-KHz bên ngồi đầu vào • Người dùng dừng q trình gỡ rối • Kích hoạt ADC - Chế độ Timer 16-bit • Chức độ định thời với chia 8-bit (cho chế độ one-shot chế độ theo chu kỳ) • Có thể lập trình one-shot thời gian • Có thể lập trình theo chu kỳ thời gian • Người dùng dừng q trình gỡ rối • Kích hoạt ADC - Chế độ Input Capture 16-bit • Capture đầu vào theo sườn • Capture đầu vào theo thơi gian - Chế độ PWM 16bit • Chế độ PWM đơn giản với đầu lập trình phần mềm tín hiệu PWM ■ Watchdog Timer - Bộ đếm xuống 32-bit với ghi tải lập trình - Xung watchdog riêng biệt - Có thể lập trình tạo ngắt - Khóa ghi bảo vệ từ phần mềm sai - Thiết lập lại logic với phép / vơ hiệu hóa - Người dùng dừng trình gỡ rối ■ ADC - Bốn kênh đầu vào analog - Cảm biến nhiệt độ bên on-chip - Tốc độ lấy mẫu 500.000 mẫu / giây - Dễ dàng cấu hình chuyển đổi tương tự - số - Linh hoạt kích hoạt điều khiển • Bộ điều khiển (phần mềm) • Timers _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 • So sánh tương tự • PWM • GPIO - Phần cứng trung bình lên đến 64 mẫu để cải thiện độ xác - Chuyển đổi sử dụng tham chiếu 3-V nội - Nguồn mass cho mạch tương tự tách biệt với nguồn mass mạch kỹ thuật số ■ UART - Hai chuẩn lập trình đầy đủ 16C550-loại UARTs với hỗ trợ IrDA - 16x8 truyền (TX) nhận (RX) FIFOs riêng biệt để giảm tải ngắt CPU - Có thể lập trình cho phép tốc độ lên tới 3,125 Mbps - Các mức độ FIFO / 8, / 4, / 2, / 4, / - Tiêu chuẩn giao tiếp không đồng với bit bắt đầu, dừng lại, tính chẵn lẻ - Phát sửa lỗi đường truyền - Lập trình đầy đủ đặc tính giao diện nối tiếp • 5, 6, 7, bit liệu • Tạo kiểm tra bit chẵn, lẻ khơng • Tạo bit dừng - Cung cấp mã hóa / giải mã IrDA serial -IR (SIR) • Lập trình sử dụng IrDA Serial Infrared (SIR) đầu vào / đầu UART • Hỗ trợ chức mã hóa / giải mã IrDA SIR cho tốc độ liệu lên đến 115,2 Kbps bán song cơng • Hỗ trợ mức lượng / 16 bình thường mức lượng thấp (1,41-2,23 μs) thời lượng bit • Có thể lập trình lấy xung clock chia 1-256 cho chế độ lượng thấp ■ Giao diện nối tiếp đồng (SSI) - Hoạt động master slave - Có thể lập trình xung nhịp tốc độ bit chia xung nhịp - Truyền nhận FIFOs riêng biệt, 16 bit rộng, vị trí sâu _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Đối với mẫu chuỗi mẫu, cấu hình nguồn đầu vào tương ứng ghi ADCSSMUXn Đối với mẫu chuỗi mẫu, cấu hình bit kiểm sốt mẫu nibble tương ứng ghi ADCSSCTLn Khi lập trình nibble nhất, đảm bảo bit END thiết lập Không để thiết lập bit END gây hành vi khơng thể dự đốn trước Nếu ngắt sử dụng, viết vào bit MASK tương ứng ghi ADCIM Kích hoạt tính xếp mẫu logic cách viết vào bit ASENn tương ứng ghi ADCACTSS 7.4 Bản đồ ghi Bảng 7.1 danh sách ghi ADC Cột offset liệt kê tăng dần theo hệ số thập lục phân địa ghi, liên quan đến địa sở ADC 0x4003.8000 Lưu ý module đồng hồ ADC phải cho phép trước lập trình ghi Đây chậm trễ hệ thống đồng hồ sau đồng hồ module ADC kích hoạt trước module ghi ADC truy cập Bang 7-1: Bản đồ ghi ADC _ 77 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Bang 7-1: Bản đồ ghi ADC (Tiếp) _ 78 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Chương VIII: UARTs Mỗi UART Stellaris có đặc điểm sau: Có hai loại lập trình đầy đủ 16C550 UARTs với trước giúp IrDA 16*8 phát nhận riêng biệt FIFOs Tốc độ Baud cho phép lên tới 3.125Mbps Chiều dài khả trình bao gồm byte vận hành sâu cung cấp giao diện đệm đôi tiêu chuẩn Các mức trigger FIFO 1/8,1/4,3/4,7/8 Các bit giao tiếp không đồng tiêu chuẩn cho start, stop parity Phát dò “line –break” Đặc tính chuỗi giao diện khả trình 5,6,7 liệu bit Bit phát/dò Even, odd, stick no-parity Phát bit stop Chuỗi IrDA-giải mã/mã hóa IR cung cấp Thiết bị khả trình sử dụng IrDA SIR vào /ra UART Trợ giúp giải mã/mã hóa IrDA SIR cho liệu lên tới 115.2Kdps bán song công Trợ giúp chuẩn 3/16 khoảng thời gian bit low-power(1.41-2.23µs) Bộ phát xung phân chia theo tói 255 cho chế độ Lowpower… _ 79 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 8.1 Sơ đồ khối Hình 8-1 Sơ đồ khối UARTs 8.2 Mơ tả chức Mỗi chức sử dụng Stellaris UART biến đổi song song sang nối tiếp nối tiếp sang song song Nó tương tự chức tới 16c550 UART, khơng ghi thích hợp UART cấu hình cho phát và/hoặc nhận thơng qua bit TXE RXE ghi UART control(UARTCTL) Việc nhận phát reset Trước ghi lập trình, UART phải bị ngắt xóa bit UARTEN UARTCTL Nếu UART bị ngắt trình vận hành TX RX, việc chuyển dịng ưu tiên hoàn thành để stop UART 8.2.1 Logic nhận/phát Logic sử dụng phát chuyển song song sang nối tiếp liệu đọc từ phát FIFO Đầu điều khiển chuỗi bit nối tiếp bắt đầu với bit start theo liệu bit (LSBfirst), bit chẵn lẻ, bit stop theo cấu hình chương trình ghi điều khiển _ 80 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 8.2.2 Tốc độ baud Bộ chia tốc độ buad số 22 bit gồm 16 bit nguyên bit phân số Các số hình thành giá trị sử dụng phát tốc đọ baud để xác định bit giới hạn Việc có chia tốc độ baud phân số cho phép UART phát tất tốc độ buad tiêu chuẩn 16 bit nguyên tải qua ghi UART integer Baud-Rate Divisor (UARRTIBRD) Bộ chia tốc độ baud có mối quan hệ tới hệ thống clock (nơi BRDI nguyên BRD NRDF phân số) BRD=BRDI+BRDF=UARTSysClk/(16*baud rate) UARTSusClk hệ thống clock nối với UART bit phân số tính tốn việc mang phân số chia tốc độ baud nhân với 64 cộng 0.5 tới phép tính cho lỗi rounding UARTFBRD[DIVFRAC]=integer (BRDF*64+0.5) Cùng ghi UART line control, high byte (UARTLCRH), dạng ghi UARTIBRD UARTFBRD ghi 30 bit nội Thanh ghi nội cập nhật vận hành write thực hiện, thay đổi tới chia tốc độ baud phải write tới ghi UARTLCRH để thay đổi ảnh hưởng Thanh ghi cập nhật tốc độ baud, có trình tự có thể: - UARTIBRD write, UARTFBRD write, UARTLCRH write - UARTFBRD write, UARTIBRD write, UARTLCRH write - UARTIBRD write, UARTLCRH write - UARTFBRD write UARTLCRH write 8.2.3 Dữ liệu phát Các liệu nhận phát lưu trữ FIFOs 16 byte, qua nhận FIFO có bit ký tự cho trạng thái thông tin Để phát, liệu viết FIFO.Nếu UART cho phép, khung liệu bắt đầu phát với thông _ 81 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 số ghi UARTLCRH Các liệu tiếp tục phát khơng cịn liệu FIFO Bit BUZY ghi UART Flags xác nhận liệu ghi FIFO Và trì liệu phát Bit BUSY FIFO trống ký tự cuối phát từ ghi dịch bao gồm bit stop UART chi bận UART khơng cịn cho phép Khi nhận khơng làm liệu vào LOW, đếm nhận bắt đầu chạy liệu lấy mẫu chu ky thứ Baud16 Bit start bật nhận dạng UnRx LOW chu kỳ baud16, khơng bỏ qua Sau bit start bật bit liệu liên tiếp lấy mẫu 16th cycle baud 16 theo chiều dài lập trình ký tự liệu Bit parity kiểm tra bit parity bật chiều dài bit liệu parity xác định ghi UARTLCRH - Bit stop xác nhận UnRx mức cao khơng có khung lỗi xảy Khi tất word nhận liệu lưu trữ nhận FIFO với lỗi liên quan tới từ 8.2.4 SIR Thiết bị ngoại vi UART bao gồm khối giải mã mã hóa IrDA SIR, Khối cung cấp chức chuyển đổi dịng UART khơng đồng giao diện bán song cơng SIR Khơng có tin tín hiệu tương tự xử lý chip Vai trò khối cung cấp đầu mã hóa số đầu vào giải mã tới UART Chân tín hiệu UART kết nối thu phát hồng ngoại để thi hành Link vật lý IrDA SIR Khối có hai chế độ hoạt động: - Chế độ bình thường IrDA : mức logic phát High 3/16 th bit tốc độ buad chọn đầu Trong logic phát tín hiệu thấp “Low” Các mẫu điều khiện điều khiển phát hồng ngoại gửi xung mẫu zero ………… - Chế độ low-power IrDA: với độ rộng xung hồng ngoại phát lần giới hạn tín hiệu phát nội IrLPBaud16 cách thay đổi bit phù hợp ghi UARTCR Trong chế độ : _ 82 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 + Trong suốt trình gửi, bit UART sử dụng cho mã hóa + Trong q trình nhận, bit mã hóa hóa chuyển tới logic nhận UART 8.2.5 Hoạt động FIFO UART có 16 FIFO trống cho phát cho nhận Tất FIFO truy cao thông qua ghi liệu UART Khi nhấn reset tất FIFO bị ngắt kết nối thực ghi giữ byte-deep FIFO cho phép việc set bit FEN UARTLCRH Trạng thái FIFOs giám sát thông qua ghi UART flag ghi UART recive status giám sát phần cứng trống, đầy, tràn Thanh ghi UARTFR bao gồm cờ trống full(TXFE,TXFF,RXFE,RXFF) ghi UARTSRS cho biết trạng thái tràn thông qua bit OE Điểm kích hoạt tải nối FIFO hoạt động ngắt điều khiển thông qua ghi UART interrupt FIFO level select UARTIFLS Tất UART kích hoạt cách riêng lẻ để kích hoạt ngắt mục khác 8.2.6 Ngắt UART ngắt điều kiện sau: Tất kiện ngắt Ored trước gửi đến điều khiển ngắt UART thực ngắt yêu cầu ngắt đơn lẻ tới điều khiển thời gian Phần mềm cung cấp dịch vụ đa ngắt chương trình ngắt việc đọc ghi (UARTIMS) Các kiện ngắt kích hoạt mức điều khiển ngắt xác định ghi UARTIM việc set bit IM tương ứng =1 Nếu ngắt không sử dụng trạng thái ngắt thô luôn đươc lên thông qua ghi UART raw interrupt status _ 83 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Ngắt luôn xóa việc set bit tương ứng ghi UART interrupt lear(UARTIC) 8.2.7 Hoạt động kiểm tra ngược UART chuyển tới chế độ lookback nội để chuẩn đoán gỡ rối Bằng việc set bit LBE ghi UARTCTL chế độ liệu truyền UnTx nhận UnRx 8.2.8 Khối IrDA sir Bao gồm giao thức mã hóa/giải mã IrDA serial IR Khi kích hoạt SIR sử dụng chân UnTx UnRx cho giáo thức SIR nên kết nối tới phát IR Khối SIR nhận phát bán song công vi thực thời gian.Việc phát bắt buộc phải dừng trước nhận liệu Tối thiểu trễ 10ms nhận phát 8.3 Khởi tạo cấu hình Để sử dụng UARTs xung ngồi phải kích hoạt việc set bit UART0 UART ghi RCGC1 Ví dụ xung UART giả định tới 20Mhz cấu hình UART là: - Tốc độ baud: 115200 - Dữ liệu: 8bit - bit stop - Không kiểm tra chẵn lẻ - FIFOs không phép - Không ngắt Việc cần xem xét lập trình UART baud rate divisor(BRD), ghi UARTIBRD UARTFBRD phải ghi trước ghi UARRTLCRH BRD tính theo cơng thức sau: BRD = 20 000 000/(16*115200) Điều có nghĩa DIVINT ghi UARTIBRD nên set =10 Giá trị tới ghi UARTFBRD tính theo cơng thức sau: UARTFBRD[DIVFRAC]=integer(0.8507*64+0.5) Với giá trị BRD tay UART cấu hình ghi tới module theo yêu cầu: o Ngắt UART việc xóa bit UARTEN ghi UARTCTL _ 84 Faculty of Electronics Engineering Ha Noi university of industry o o o o FEE2-K2 Viết phần nguyên BRD vào ghi UARTIBRD Viết phần thập phân BRD vào ghi UARTFBRD Viết thông số mong muốn vào ghi UARTLCRH Cho phép UART việc set bit UARTEN ghi UARTCTL _ 85 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Chương IV: Một số hình ảnh LM3S8962 Hình 9.1: Sơ đồ chân LM3S8962 _ 86 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Kết luận Nghiên cứu ban đầu cho thấy kết khả quan, tạo tiền đề cho phát triển ứng dụng với ARM Cortex M3 Để phát triển đề tài này, xin đưa số ưu nhược điểm sau: Ưu, nhược điểm: Ưu điểm Giá thành chip rẻ so với dòng chip khác với số tài nguyện ARM Tốc độ xử lý cao, ổn định Tiết kiệm lượng Số lượng tài nguyên lớn, phù hợp với nhiều ứng dụng khác Nhược điểm Nhiều ghi, câu lệnh dài, gây khó nhớ cho người dùng, dễ nhầm lẫn Thị trường ARM Việt Nam chưa rộng, gây khó việc tìm kiếm tài liệu khó khăn việc đặt mua chip, việc nghiên cứu chưa sâu Hướng phát triển: Đặt mua KIT từ TI tạo điều kiện nghiên cứu thực tế module Tạo module thực tế để tạo điều kiện thuận lợi cho sinh viên nghiên cứu, thực hành với ứng dụng thực tế, dễ hình dung _ 87 Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 Tài liệu tham kho Datasheet Stellarisđ LM3S8962 Microcontroller - Copyright â 2007-2011 Texas Instruments Incorporated StellarisWare® Software from website http://www.ti.com/stellaris _ 88 Faculty of Electronics Engineering ... Engineering Ha Noi university of industry FEE2-K2 Chương I: Tổng quan kiến trúc ARM Cortex M3 Các dòng vi điều khiển Stellaris – ARM ® ™ Cortex- M3 - mang lại ứng dụng vi điều khiển nhúng hiệu suất cao... GPTM TimerB Chương III: Cấu trúc hoạt động Interrupts 3.1 Xử lý ngắt Một cải tiến quan trọng Cortex so với CPU ARM trước cấu trúc ngắt xử lý ngắt ngoại lệ Với ARM7 ARM9 thường có đường ngắt: ngắt... khiển LM3S8962 bao gồm tính sau: ■ 32-bit RISC _ Faculty of Electronics Engineering Ha Noi university of industry FEE2-K2 - 32-bit ARM Cortex ® ™ -M3 v7M kiến trúc

Ngày đăng: 18/02/2014, 14:00

Xem thêm: tổng quan kiến trúc arm cortex m3